놀랍게도 10년 가까이 UFS 관련 개발을 해왔는데, 관련 포스팅이 여태까지 1개도 없었다는 게 내가 생각해도 신기하네...

(그림 출처: https://www.storagenewsletter.com/2016/04/07/jedec-publishes-jesd220-2-universal-flash-storage-card-extension-standard/)

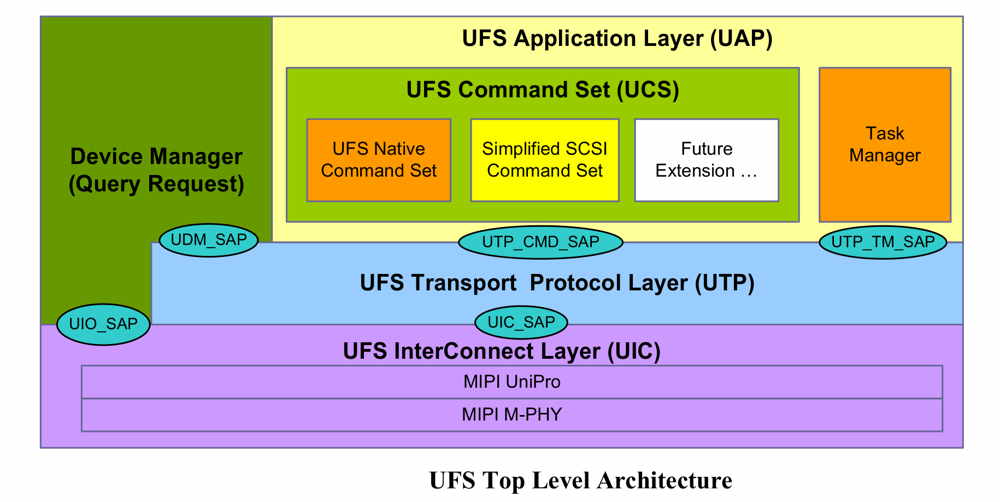

위는 UFSHCI(host controller interface) 등 ufs 스펙에 주로 표현되는 내용이다.

공학을 전공하거나 통신 관련 내용을 접해봤다면 상당히 익숙할 구조이다. 많은 analog/physical 및 프로토콜 기반 통신을 지원하는 고속 장치 들은 OSI 7 Layer 의 형태로 구현된다. ufs 도 이와 유사하다.

간략한 특징은 아래와 같다.

- 이름의 의미처럼 Mobile/Embedded Application 향 가장 보편화된 Flash Memory이다

- eMMC를 대체할 제품이었으며 대부분의 portion을 차지하나, 전부는 아니다. 저가형 application 및 일부 시장의 경우 아직 eMMC가 점유하고 있다.

- 현재 Jedec 기준 ufs 4.0까지 표준 스펙이개발 되었다. 실제 메모리 회사들의 제품도 ufs 4.0 스펙을 준수하는 제품들이 개발/판매 되고 있다.

- device manager (query commands set) : flag/atteibute/descriptor 등을 지원하며 ufs device 의 configuration 을 위한 interface가 주로 정의/지원되고 있다. lu provisioning 및 feature on/off 등

- UAP - task manager(abort command set) : command set 그대로 traffic 중인 command 들의 강제종료 등의 control을 위한 interface이다.

- UAP - UCS (scsi command set) : 실제 사용되는 command 는 scsi set이다. linux kernel 내에도 scsi midlayer 의 low level device 로 소속되어있다. 최근 source path는 scsi 를 벗어 났는데(drivers/scsi/ufs -> drivers/ufs), 어떤 의도인지는 두고봐야 알 일이다.

일반적인 내용을 기준으로 차차 정리해보도록 하겠다.

UFS 는 Android 와 같은 embedded system 로 현재 보편적으로 탑재되고 있으며 보다 세부적인 구조는 아래와 같다.

- Application Software : 일반적인 사용자/시스템 프로그램 들이며 android의 경우 실제 앱 들이라고 볼 수 있다.

- OS/Common UFS Host Controller Driver : File System, Block IO 및 scsi driver 와 이를 통해 Host-side의 UFSHCI를 제어하여 동작하는 low level device driver이다.

- UFS Host Controller : ARM 및 Intel 등 SoC 및 CPU 내에서 UFS device 와 통신 할 수 있는 Host side IP이며, 이를 Host Controller 라 한다. data i/o 등의 scsi command set, query 등의 ufs control command set 및 uic command 등을 통해 flash memory 를 제어한다. interconnect 라 모호하게 표기되어 있으나 앞선 포스팅에서 살펴본 바와 같이 mphy 및 unipro 와 기타 프로토콜 레이어가 ip로 구현되어 있다.

- UFS Mass Storage Device : 통상적으로 UFS 라고 부르는 실제 스토리지 디바이스인 메모리 반도체, 그 녀석이다. 플래쉬 메모리. HCI와 대칭되는 IP 구조를 갖고 있으며(interconnect 가 대칭적으로 표현된 것이 그러한 의미로 ufs 도 동일하게 mphy/unipro 등이 구현되어 있다-통신을 하려면 당연히 프로토콜이 pair여야 하니까), 내부적으로는 flash memory이니 당연히 nand flash가 controller chip 과 함께 packaging 되어 있으며, UFSHCI를 통해 전달 되는 data read/write 및 Host(OS 등)의 configuration/request를 처리/응답하고 있다.

개요는 이쯤이면 될 듯 하고, 이후로는 Host / OS driver 등 Software 관점에서 살펴보도록 하겠다.

덧) 개요 내용 중 추가가 필요한 부분이 있다. HCI 세부 내용이라 덧붙인다.

- IO memory/register space : HCI는 MMIO 구조로 구성되어 주로 AP나 controller 의 Host side 구현 사항으로 이해할수있다.

- Host Memory Space : 여기서는 여러가지 부분으로 나뉘어 지는 데, 실제 device driver는 IP와 디자인 히드웨어 대한 OS 관점의 control 이 주가 되므로 잘 이해하는 것이 중요하다.

- UTRL(UTP transfer request list) : SCSI 및 Query command set 에 대한 부분으로 0~31, 즉 32 개의 command 가 동시에 queueing 될 수 있다. 각 descriptor 는 cdb 정보를 담고 있는 command upiu 와 command 의 response data를 담게 될 response upiu, traffic data 를 처리할 PRDT 및 실제 Data buffer(dma type memory) 를 포함한다.

- UTMRL(UTP task management request list) : task management 는 queueing 된 command 를 취소/종료를 처리하는 게 주된 목적으로 별도의 data buffer 가 필요 없다. 또한 많은 command queueing 도 필요 없어 0~7, 즉 8개의 command 만 처리되도록 지원한다. 그런고로 각 command 도 간순하게 request/response upiu만 존재한다.

출처: https://chlrbgh0.tistory.com/451 [think of me:티스토리]

'Embedded : : Arm Architecture > : : Peripheral' 카테고리의 다른 글

| PCIe 용어와 특징 (0) | 2024.11.12 |

|---|---|

| PCIe states (0) | 2024.11.12 |

| PCIe Interrupt (0) | 2024.11.12 |

| DSI / CSI (0) | 2024.11.07 |

| MCU : DIE, PAD, Drive Strength, Pad Level, Hysteresis (0) | 2024.05.04 |