1. Exception Model

1.1 익셉션 모델

익셉션은 시스템 흐름에서 벗어나 익셉션 핸들러의 처리를 필요로하는 상태 or 시스템 이벤트

1.2 익셉션 모델이 정하는 것들

- 익셉션 타입과 상태

- 프로세서의 익셉션 핸들링 루틴

- 익셉션 복귀

2. 익셉션 레벨 (Exception Level)

2.1 익셉션 레벨이란

2.2 Exception Level별 동작

EL0 : 유저 어플리케이션

EL1 : 커널

EL2 : 하이퍼바이저

EL3 : 보안 모니터

2.3 프로세스 동작상태

EL3가 상태를 전환하는데, 시큐리티 상태에 따라 나뉨

1) non-secure (normal 상태) : 물리 메모리 접근 불가능

2) secure

2.4 익셉션 레벨 변경

익셉션이 발생되면 같은 익셉션 레벨이나 높은 익셉션 레벨로 이동함

의도하지 않은 권한 상승이 발생하면 안되므로, 익셉션이 발생한 레벨보다 낮은 레벨에서는 익셉션이 발생하지 않음

즉, EL0은 익셉션핸들링이 불가능하므로EL0에서 발생한 익셉션은 EL1에서 핸들링 함

2.5 익셉션 레벨 상황

익셉션 핸들링이 끝나고 기존 실행 코드로 돌아갈 땐 ERET 인스트럭션을 명시적으로 사용해야함

익셉션 복귀 시 익셉션 발생과 반대로 동일한 익셉션 레벨이나 낮은 익셉션 레벨로 이동

- *IRQ와 FIQ 인터럽트 시그널

- 메모리 시스템 *abort

- 정의되지 않은 인스트럭션 실행

- 시스템 콜

- 보안 모니터나 하이퍼바이저 트랩

*IRQ : Interrupt Request / PC내부의 어떤 장치가 시스템에 자기가 System의 어떤 부분을 사용하기 위해 system Call을 하는 것

*abort : 프로그램 비정상 중단/종료,, 호스트환경에 제어를 리턴 ,, abort()함수 호출 시 SIGABRT 신호가 발생함

2.6 실행상태

|

AArch64

|

AArch32

|

|

|

특징

|

64bit 실행환경

|

32bit 실행환경

|

|

레지스터

|

- 64bit 크기의 범용 레지스터 31개

- PC(Program Counter)

- SP(Stack Pointer)

- ELR(Exeception Link Register)

|

- 32bit 크기의 범용 레지스터 13개

- PC(Program Counter)

- SP(Stack Pointer)

-LR(Link Register)

|

|

인스트럭션 세트

|

A64 (32bit 인코딩)

|

T32 (Thumb)

A32 (ARMv7지원)

|

|

주소 방식

|

64bit 가상주소

|

32bit 가상주소

|

|

익셉션 모델

|

ARMv8 익셉션모델(EL0~EL3)

|

ARMv7 익셉션 모델 (ARMv8에 매칭됨)

|

※ Program Counter

프로그램 카운터는 실행중인 코드의 주소를 가리키고, 어셈블리 명령어 실행시 4byte만큼 ARM Processor가 증가시킨다.

레지스터는 다음에 실행할 인스트럭션 위치를 저장하는 레지스터다.

ARMv8에서 PC레지스터는 프로그래머가 직접 접근하지 못한다. 대신 PC로드와 상대 주소 지정같은 인스트럭션에서 내부적 사용된다.

3. ARMv8 레지스터

3.1 ARMv8 레지스터

→ 하나의 단일레지스터 세트를 모든 익셉션 레벨에서 사용 가능하도록 변경한 것

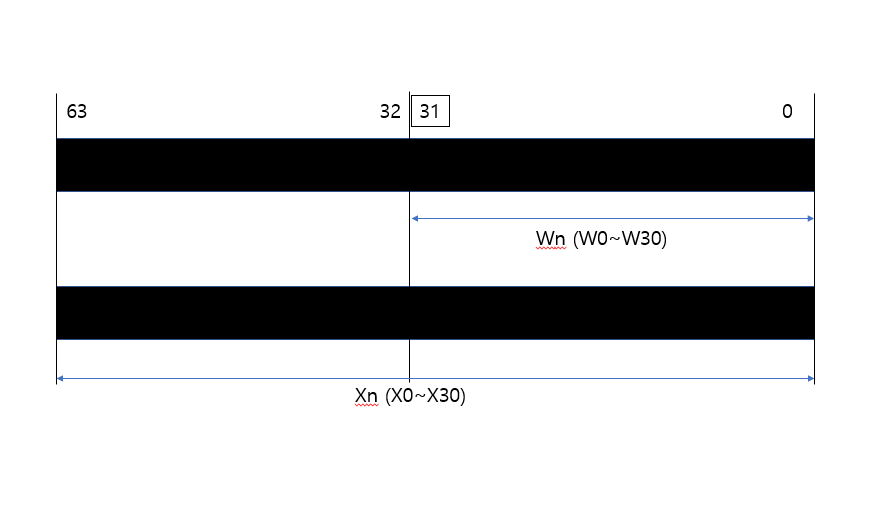

- 범용 레지스터에 접근할 때 X0~X30이라는 이름으로 지정하면 64bit를 모두 사용

- W0~W30이라는 이름으로 지정하면 이 중 하위 32bit만 사용

3.2 PSTATE (프로세스 상태 레지스터)

PSTATE는 프로세서 상태 정보를 제공하는데, AArch64전용, AArch32전용, AArch 64와 32 공통속성으로 구성된다.

3.3 System Register (시스템 레지스터)

AArch64에서 시스템 설정은 각 시스템 레지스터를 통해 제어되며, MSR 및 MSR 인스트럭션을 사용하여 접근 할 수 있다.

4. AArch64 익셉션 핸들링

AArch64 익셉션 핸들링 유형

1) 서비스 호출 인스트럭션 익셉션

2) abort 익셉션

3) 리셋 익셉션

4) 인터럽트 익셉션

4.1 서비스 호출 인스트럭션 익셉션

SW에서 좀 더 높은 특권레벨에서 동작하는 서비스를 요청하기 위해 호출됨

* SVC (Supervisor Call) : 유저모드 프로그램에서 OS서비스를 요청할때 사용

* HVC (Hypervisor Call) : 게스트 OS에서 하이퍼바이저 서비스 요청 시 사용

* SMC (Secure Monitor Call) : 일반구역에서 보안구역 서비스를 요청할때 사용

4.2 abort 익셉션

리눅스는 MMU abort를 이용해 *디맨드 페이징을 구현함

* 디맨드 페이징 : 메모리 관리 메커니즘 (MMU 메커니즘)을 사용해 여러 프로세스가 시스템의 메모리를 효율적으로 공유할 수 있도록 하는 기술

발생 원인

1. Instruction fetch가 실패할 경우 발생하는 인스트럭션

2. abort의 데이터 접근이 실패할 경우 발생하는 abort

3. MMU의 메모리 접근이 실패할 경우 발생

동기식과 비동기식

- 동기식 abort : 인스트럭션스트림의 실행 또는 시도에 의해 생성되고, 리턴 주소가 abort를 초래한 인스트럭션의 세부사항을 제공

- 비동기식 abort : 인스트럭션의 실행으로 생성 X, 리턴주소는 중단 원인에 대한 세부정보 제공 X

4.3 리셋 익셉션

전원을 켠 후 코어를 초기화하는 코드를 실행하는데 사용. 코어에 리셋이 입력되면 발생한다.

- 리셋 익셉션이 발생하면 코어는 리셋 벡터로 점프

리셋 벡터에는 실행할 인스트럭션의 주소를 저장

RVBAR_ELn 레지스터가 리셋 벡터를 기록하기 위해 사용

4.4 인터럽트 익셉션 / 인터럽트 핸들러

ARM 아키텍처의 인터럽트는 IRQ와 FIQ로 나뉘며, 우선순위는 FIQ > IRQ 순이다.

인트럽트는 인터럽트 컨트롤러와 코어를 연결한 IRQ, FIQ 라인을 통해 물리적 신호로 전달된다.

인터럽트 컨트롤러는 연결된 각 디바이스에 인터럽트 신호를 중재하고 우선순위를 지정하여 최종적으로 직렬화 된 단일 신호로 각 코어의 IRQ 또는 FIQ로 전달한다.

인터럽트가 발생하면 이를 처리하기 위한 핸들러

동기 및 비동기 익셉션

|

동기 익셉션

|

비동기 익셉션

|

|

|

익셉션 발생 원인

|

인스트럭션 실행 또는 실행 시도의 결과로 발생

|

인스트럭션의 실행과 무관

|

|

익셉션 정보

|

리턴 주소는 익셉션을 발생시킨 인스트럭션

|

리턴 주소가 익셉션 원인에 대한 정보를 제공하지 않을 수 있음

|

|

인터럽트 소스

|

- MMU 인스트럭션, 데이터 abort

- PS, SP의 정렬 위반

- 동기 외부 abort

- 할당되지 않은/ 허용하지 않은 인스트럭션 발생

- 디버그 익셉션

|

- IRQ

- FIQ

- SError

|

동기 익셉션은 익셉션 원인을 핸들러에서 알 수 있도록 ESR-ELn(Exception Syndrome Register) 레지스터가 제공됨

'Embedded : : Arm Architecture > : : Arm Architecture' 카테고리의 다른 글

| ARMv8 Intro. (0) | 2024.11.06 |

|---|