12.1 Intro

이 장에서는 LVDS 인터페이스를 지원하는 i.MX 레퍼런스 보드에 LVDS 패널을 연결하는 방법을 설명합니다. 현재 IPU가 탑재된 i.MX 6 및 i.MX 8QuadMax, i.MX 8QuadXPlus, i.MX 8M Plus 및 i.MX 93은 LVDS 디스플레이 인터페이스를 지원합니다. i.MX 8 및 i.MX 93용 DRM driver와 i.MX 6용 framebuffer driver로 LVDS를 구현합니다. LVDS는 i.MX 8 및 i.MX 93용 DRM LDB driver와 i.MX 6용 framebuffer driver로 구성된 LVDS Display Bridge(LDB)에 연결됩니다.

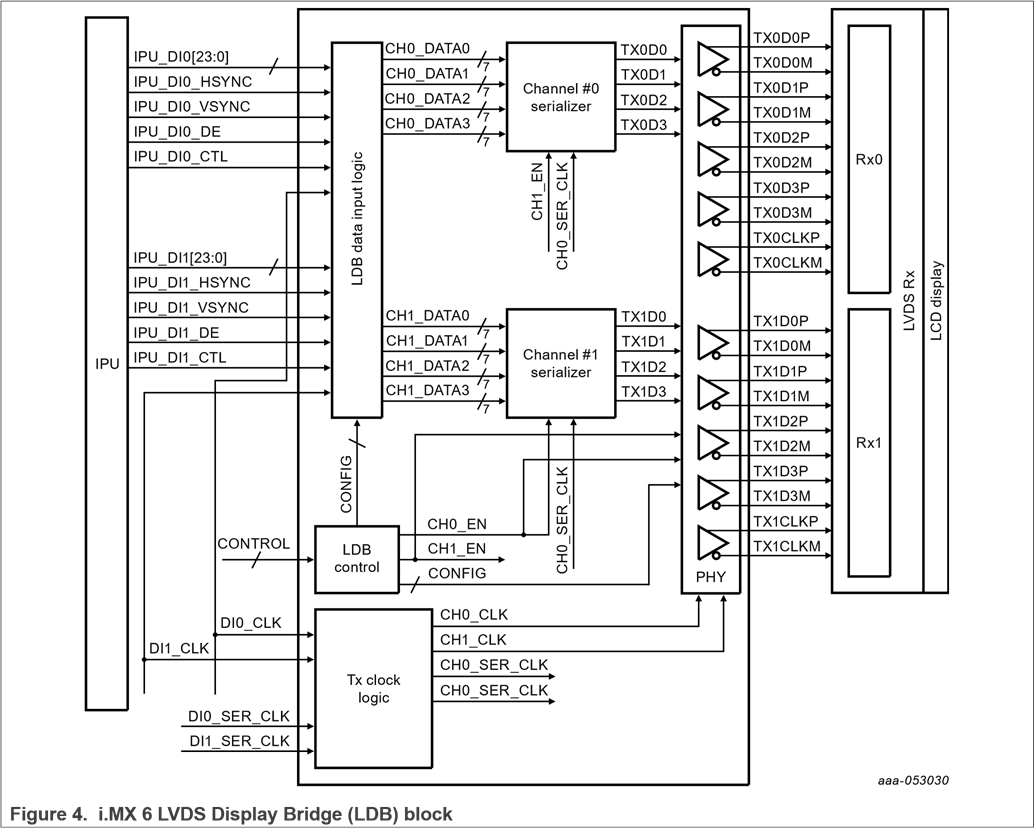

IPU가 탑재된 i.MX 6에는 외부 브리지 없이 LVDS 패널을 구동하는 LDB(LVDS Display Bridge) 블록이 있습니다. IPU가 있는 i.MX의 LDB는 LVDS 인터페이스를 통해 IPU에서 외부 디스플레이 장치로의 동기식 RGB 데이터 흐름을 지원합니다.

LDB 지원에는 다음 활동이 포함됩니다.

• LVDS 수신기를 사용하여 관련 장치 디스플레이에 연결합니다.

• 외부 디스플레이 수신기 및 LVDS 디스플레이 표준에 따라 데이터를 정렬합니다.

• 동기화 및 제어 기능.

12.1.1 Connecting an LVDS panel to the i.MX 8 and i.MX 93

i.MX 8, i.MX 8M Plus 및 i.MX 93의 LVDS 인터페이스는 DRM 디스플레이 프레임워크로 구현됩니다. 이 LVDS 인터페이스는 it6263 인코더를 사용하여 i.MX QuadMax의 Mixel 및 i.MX 8QuadXPlus의 Mixel Combo와 함께 작동합니다. LVDS 인터페이스는 i.MX 93에서 NXP가 설계한 LVDS PHY와 함께 작동하며 it6263 브리지와 연결할 수 있습니다. 둘 다 1080p 해상도를 지원합니다. it6263에 대한 연결은 arch/arm64/boot/dts/freescale의 커널 저장소에 있는 fsl-imx8qxp-mek-it6263-lvds0-dual-channel.dts와 같은 디바이스 트리를 통해 설정됩니다.

12.1.2 Connecting an LVDS panel to the i.MX 6

24비트 LVDS 패널(4쌍의 LVDS 데이터 신호)에 대한 커널 명령줄은 패널이 제대로 연결된 경우 다음 줄을 표시합니다.

video=mxcfb0:dev=ldb,if=RGB24

18비트 LVDS 패널(LVDS 데이터 신호 3쌍)에 대한 커널 명령줄은 패널이 제대로 연결된 경우 다음 줄을 표시합니다.

video=mxcfb0:dev=ldb,if=RGB666

12.2 LDB로 LVDS 채널 활성화

mxc 디스플레이 코어 드라이버가 LDB 장치를 검색할 때, 드라이버는 DTS 파일의 플랫폼 데이터 정보를 사용하여 LDB의 reference sistor mode를 구성하고 외부 디스플레이 장치의 비디오 모드를 LVDS 인터페이스와 일치시키려고 시도합니다. 디스플레이 신호 극성과 LDB 제어 비트는 일치하는 비디오 모드에 따라 설정됩니다.

LVDS 채널 매핑 모드와 LDB의 LDB 비트 매핑 모드는 사용자가 설정한 LDB 장치 트리 노드에 따라 설정됩니다.

LVDS 채널은 다음과 같이 활성화됩니다.

1. ldb_di_clk의 상위 클럭과 상위 클럭 속도를 설정합니다.

2. ldb_di_clk의 속도를 설정합니다.

3. 디스플레이 신호의 극성, LVDS 채널 매핑 모드, 비트 매핑 모드 및 기준 저항 모드를 포함하여 LDB를 적절한 모드로 설정합니다.

4. ldb_di_clk와 해당 상위 시계를 모두 활성화합니다.

12.3 i.MX 6의 LDB 포트

다음 그림은 LDB 블록을 보여줍니다.

LDB에는 다음과 같은 포트가 있습니다.

• 2개의 입력 병렬 디스플레이 포트

• 2개의 출력 LVDS 채널

• LDB 매개변수 및 작동을 구성하는 제어 신호

• SoC PLL의 클록

12.3.1 LDB on i.MX 6 for input parallel display ports

LDB는 1개 또는 2개(DI0, DI1) 병렬 RGB 입력 포트를 지원하도록 구성할 수 있습니다. LDB는 동기 액세스 모드만 지원합니다.

각 RGB 데이터 인터페이스에는 다음이 포함됩니다.

• 18 또는 24비트의 RGB 데이터

• 픽셀 시계

• 제어 신호

• HSYNC, VSYNC, DE 및 추가 범용 제어 옵션 1개

• 픽셀 클록 사이클당 데이터 인터페이스당 최대 28비트를 전송합니다. LDB는 다음 데이터 속도를 지원합니다.

• 듀얼 채널 출력의 경우: 최대 170MHz 픽셀 클록(예: 60Hz + 35% 블랭킹에서 UXGA-1600 x 1200)

• 단일 채널 출력의 경우: 인터페이스당 최대 85MHz(예: 60Hz + 35% 블랭킹에서 WXGA-1366 x 768).

12.3.2 LDB on i.MX 6 Output LVDS ports

LDB로 LVDS 채널 활성화 LDB에는 LVDS 인터페이스나 LVDS 수신기를 통해 RGB 데이터 및 컨트롤을 외부 LCD 디스플레이에 전달하는 데 사용되는 두 개의 LVDS 채널이 있습니다. 각 채널은 4개의 데이터 쌍과 1개의 클록 쌍으로 구성되며, 한 쌍은 PadP 및 PadM을 포함하는 LVDS 패드를 나타냅니다.

LVDS 포트는 다음과 같이 사용될 수 있습니다:

• 단일 채널 출력 1개

• 1개의 듀얼 채널 출력: 단일 입력, 2개의 출력 채널로 분할

• 두 개의 동일한 출력: 두 출력 채널 모두에 단일 입력이 전송됩니다.

2개의 독립적인 출력: 2개의 입력이 각각 별도의 출력 채널로 전송됩니다.

'SoC : : Architecture > : : i.MX93' 카테고리의 다른 글

| i.MX 9 BSP Porting Guide - Supporting Cameras with CSI (0) | 2024.04.30 |

|---|---|

| i.MX 9 BSP Porting Guide - Connection MIPI-DSI Panel (0) | 2024.04.30 |

| i.MX 9 BSP Porting Guide - Configuring SPI NOR (0) | 2024.04.30 |

| i.MX 9 BSP Porting Guide - Adding SDHC (0) | 2024.04.30 |

| i.MX 9 BSP Porting Guide - UART (0) | 2024.04.30 |